Product Summary

The XC4013XL-1BG256C Field-Programmable Gate Array (FPGA) provides the benefits of custom CMOS VLSI, while avoiding the initial cost, time delay, and inherent risk of a conventional masked gate array.

Parametrics

Absolute maximum ratings: (1)Propagation Delays: Pad to I1, I2: 2.5 ns, Pad to I1, I2, via transparent latch (no delay): 3.6 ns, Pad to I1, I2, via transparent latch (with delay): 7.1 ns, Clock (IK) toI1, I2, (flip-flop): 2.8 ns, Clock (IK) to I1, I2 (latch enable, active Low): 3.0 ns; (2)Set-up Time: Pad to Clock (IK), no delay: 4.7 ns, Pad to Clock (IK) with delay: 8.3 ns; (3)Hold Time: Pad to Clock (IK), no delay: 0 ns, Pad to Clock (IK) with delay: 0.

Features

Features: (1)Flexible Array Architecture: Programmable logic blocks and I/O blocks, Programmable interconnects and wide decoders, Sub-micron CMOS Process; (2)High-speed logic and Interconnect; (3)Low power consumption; (4)Systems-Oriented Features: IEEE 1149.1-compatible boundary-scan logic support, Programmable output slew rate (2 modes), Programmable input pull-up or pull-down resistors, 12-mA sink current per output, 24-mA sink current per output pair.

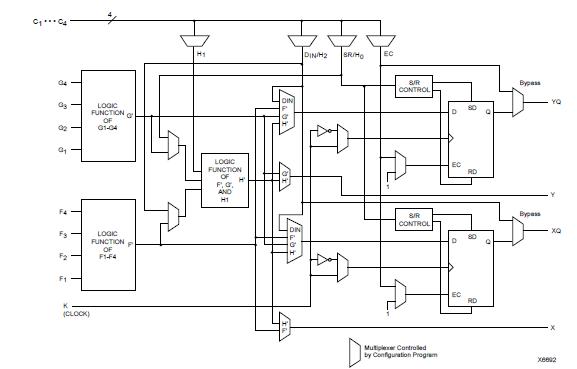

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

XC4013XL-1BG256C |

|

IC FPGA C-TEMP 3.3V 1SPD 256PBGA |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

XC4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000XL |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))